IP-Stack für SmartCards

Projektbeschreibung

Eine immer wichtiger werdende Aufgabe in der Entwicklung von Smart Card Systemen ist die Vernetzung dieser mit dem Internet. Die Integration einer Smart Card als Security Token würde eine Reihe von neuen Anwendungsfeldern ermöglichen. Viele Internet-Dienste könnten von dem hohen Sicherheitsmaß, welche eine Smart Card bietet, besonders bei der Authentifikation oder Speicherung bzw. Verarbeitung von sensiblen Daten profitieren. So sind beispielsweise TLS-Tunnel oder sichere Proxys über Smart Cards ein interessantes Einsatzgebiet. Auch die Entschlüsselung von sensiblen Daten-Strömen, auf der Basis von Nutzer Zertifikaten, stellt für zukünftige Smart Card Generationen ein mögliches Einsatzgebiet dar.

Internet-Protokoll Stack für Smart Cards

Um diese Technologien zu ermöglichen, ist es jedoch notwendig bestehende Kommunikationsprotokolle in die Funktionalität einer Smart Card zu integrieren. In diesem Projekt, in Kooperation mit der Firma Morpho e-Documents Paderborn, wurde daher ein konfigurierbarer Internet Protokoll Stack für Smart Cards entwickelt. Bei dem IP-Stack handelt es sich um einen voll funktionsfähigen Protokoll Stack, welcher dem vom Europäischen Institut für Telekommunikationsnormen (ETSI) definierten Standard TS 102 483 für die „IP-Konnektivität zwischen Smart Card und Terminal“ entspricht.

Optimierung und Re-Konfiguration

Bei der Entwicklung stellte die Optimierung des statischen sowie dynamischen Speicherbedarfs das größte Problem dar. Im Verlaufe des Projektes kamen daher zum einen Konfigurationsmechanismen auf Quellcode-Ebene wie z.B. Präprozessor-Makros zum Einsatz. Ein speziell entwickeltes Tool erlaubt durch Angabe von Kommunikationsparametern eine genaue Anpassung des IP-Stacks an ein gegebenes Einsatzgebiet. So können sehr geringe Speichergrößen bereits auf statischem Level erreicht werden, welches den nativen Einsatz von Internet Protokoll Techniken bereits auf heutigen Smart Cards erlaubt.

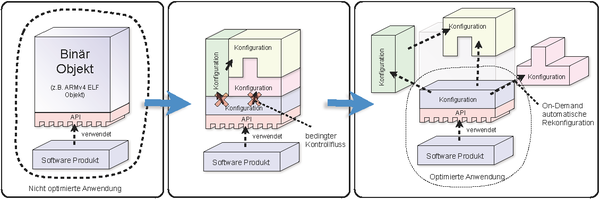

Diese Art der Konfiguration beschränkt sich jedoch auf Funktionalitäten, welche auf der Ebene des Quellcodes vorhanden und modifiziert werden können. Da aber fast immer auf proprietäre Funktionalitäten, zumeist durch Bibliotheken, zurückgegriffen wird, bestand der weitere Fokus des Projektes auf der Erforschung von Mechanismen zur Optimierung dieser binären Objekte. Das entwickelte Verfahren ermöglicht es binäre Objekte durch einen eigens entwickelten Link-Time Optimierer an ein gegebenes Einsatzgebiet anzupassen. Hierfür werden High-Level Informationen aus den binären Objekten extrahiert, gegen Bedingungen des Einsatzgebietes geprüft und Konfigurationen gebildet, welche statisch entfernt und zur Laufzeit nachgeladen werden können. Die Konfigurationen werden dabei automatisch identifiziert, entfernt und für einen späteren Nachlade-Prozess neugeschrieben. Im Moment wird hierfür die ARMv4(t) ISA unterstützt. Das Verfahren kann in Zukunft jedoch auf weitere Architekturen erweitert werden. Auch wenn diese Technik innerhalb des IP-Stack Projektes erfolgreich erprobt wurde, ist der Ansatz nicht auf dieses spezielle Gebiet beschränkt.

Validierung

Im letzten Teil des Projektes wird aktuell eine TTCN3 basierte Test Umgebung entwickelt um den entwickelten IP-Stack (optimiert und unoptimiert) gegen seine Spezifikation zu prüfen. Hierfür werden spezielle TTCN3 Test Cases für die eingesetzten Protokolle entwickelt (IPv4,IP46,TCP,TLS..) und ein Test Adapter für die automatisierte Ausführung dieser Tests entwickelt.

Organisation

Wissenschaftliche Leitung:

Prof. Dr. Franz Josef Rammig, s-lab

Kontakt:

Dr. Stefan Sauer, s-lab

Universität Paderborn

Zukunftsmeile 1 - ZM1.03-44

33102 Paderborn

| Telefon: | (+49) (0) 5251 60 - 5390 |

| Fax: | (+49) (0) 5251 5465 - 282 |

| E-Mail: | sauer[at]s-lab.uni-paderborn.de |

Projektpartner:

Morpho e-Documents Paderborn

Literatur

- Daniel Baldin, Stefan Groesbrink, Timo Kerstan, Simon Oberthür:

Towards Constraint-based Binary Code Optimization using Annotated Control Flow Graphs.

In Proceedings of the 2nd International Conference on Advances in Distributed and Parallel Computing (ADPC), Global Science and Technology Forum, vol. 2, 2011, pp. 59-64 - Daniel Baldin, Stefan Groesbrink, Simon Oberthür:

Enabling Constraint-based Binary Reconfiguration by Binary Analysis.

In International Journal on Computing (JoC), vol. 1, no. 4, 2011 - TTCN3 Spezifikation (Link)